IC được coi là yếu tố chủ yếu quyết định giá thành của bộ linh kiện, chính vì vậy muốn chủ động trong việc sản xuất ra sản phẩm ta cần phải chủ động sản xuất linh kiện như IC. Cùng VANDA tìm hiểu quy trình sản xuất nhé!

Giới thiệu chung

Giới thiệu qui trình sản xuất IC bắt đầu từ phiến siliconQui trình sản xuất IC bắt đầu từ phiến silicon đến việc ra sản phẩm cuối cùng. Tuy nhiên, với mỗi hãng sẽ chọn cách thức tạo ra sản phẩm riêng, có thể là cả quá trình từ khi bắt đầu tạo chip cho đến khi tạo ra một sản phẩm hoàn chỉnh, cũng có thể là mua phôi trắng từ các hãng khác và về đóng gói, thiết kế thành sản phẩm của mình.

Intel, AMD hoặc là Renesas là các chipmaker, tức là tạo sản phẩm từ miếng silicon. Qui trình sản xuất của các hãng nhìn chung như sau.

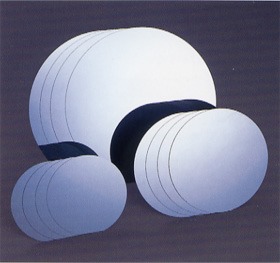

Tấm silicon - vật liệu ban đầu dùng trong ngành công nghệ vi điện tử là các phiến silicon (silicon wafer) có bề dày cỡ 400 micro-mét với đường kính khác nhau (tấm silicon có đường kính lớn nhất mà người ta có thể chế tạo là 12 inch, nghĩa là tương đương một chiếc piza lớn). Tấm silicon có đường kính càng lớn thì càng khó chế tạo, thiết bị dành cho công nghệ tấm lớn càng tốn kém nhưng số linh kiện thu được trên một tấm lại được nâng cao.

Phòng sạch - Mọi quá trình công nghệ chế tạo mạch tổ hợp được tiến hành trong phòng sạch. Đó là nơi con người cần phải xử lý các thông số môi trường như nhiệt độ, độ ẩm và lưu thông khí sao cho số hạt bụi có trong một đơn vị thể tích là nhỏ hơn rất nhiều so với môi trường bình thường. Độ sạch của phòng sạch khi được chế tạo phải tuân thủ những tiêu chuẩn ISO khác nhau (từ ISO 1 đến ISO 9 trong đó ISO 1 có độ sạch cao nhất tương đương với 10 hạt bụi kích thước nhỏ hơn 0.1 micron trong một phút khối) độ sạch càng lớn thì chi phí vận hành càng tốn kém.

Xử lý bề mặt - đó là viiệc đầu tiên người làm công nghệ cần thực hiện trong phòng sạch. Công đoạn làm sạch bề mặt phiến (silicon) thường được thực hiện nhờ các axit mạnh, các chất có tính ôxi hoá như HNO3, H2SO4 H2O2 và HF. Việc xử lý bề mặt sẽ giúp chúng ta loại bỏ những tạp vô cơ, hữu cơ hoặc sai hỏng trên bề mặt tấm silicon trước khi chuyển nó vào những bước công nghệ tiếp theo.

Ôxi hoá - trong quá trình chế tạo mạch tích hợp người ta thường phải dùng lớp SiO2 trên bề mặt tinh thể Si.. Lớp SiO2 này có hệ số dãn nở nhiệt gần bằng hệ số giản nở ~ 4, có tác dụng bảo vệ bề mặt các linh kiệnenhiệt của Si, với hằng số điện môi bán dẫn dưới tác dụng của môi trường bên ngoài, che chắn bề mặt Si trong quá trình khuếch tán định xứ các tạp chất như P và B. Ngoài ra lớp SiO2 còn được sử dụng làm cực (gate) cửa cho bóng bán dẫn (transistor). Có nhiều phương pháp tạo ra lớp SiO2 nhưng phương pháp được sử dụng rộng rãi nhất để nhận lớp SiO2 là phương pháp ôxy hoá ở nhiệt độ cao (khoảng 10000C -11000C).

Khuếch tán - là kỹ thuật được sử dụng trong công nghệ bán dẫn để tạo các vùng chuyển tiếp của transitor. Có nhiều phương pháp để khuếch tán tạp tạo vùng chuyển tiếp P-N khác nhau như phương pháp khuếch tán ở nhiệt độ cao, phương pháp cấy ion... Tuỳ thuộc vào đế silicon và mục đích của việc pha tạp người làm công nghệ sẽ phải dùng hai loại tạp phổ biến nhất là Boron (B) hoặc phốtpho (P) cho quá trình này.

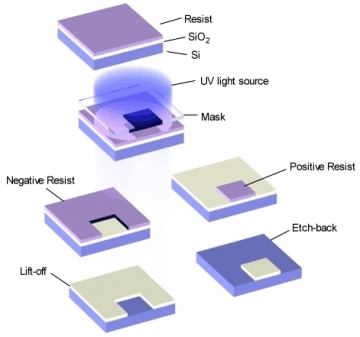

Quang khắc (photolithography) - là tập hợp các quá trình quang hoá nhằm tạo ra các chi tiết trên bề mặt phiến silicon có kích thước và hình dạng giống như thiết kế. Để làm được điều này cần phải có những bộ mặt nạ (mask), chất cảm quang (photoresist) nguồn sáng UV và dung dịch hiện hình (developer). Mặt nạ thường là một tấm thuỷ tinh hữu cơ được phủ một màng crôm trên đó khắc hoạ những chi tiết phù hợp với thiết kế của cảm biến hoặc mạch tích hợp (IC).

Người ta phủ lên trên bề mặt phiến silicon có tính chất nhậy sáng đặc biệt gọi là chất cản quang (photoresist) – thường được gọi là chất cảm quang. Chất cảm quang phải bảo đảm hai tính chất: - Nhậy quang; - Bền vững trong các dung môi axít hoặc kiềm. Chất cảm quang có nhiệm vụ là lớp bảo vệ có hình dạng cần thiết cho bề mặt khỏi bị tác dụng của các dung môi hoá học. Người ta phân loại cảm quang thành cảm quang dương và cảm quang âm dựa vào cơ chế phản ứng xẩy ra trong cảm quang khi bị chiếu sáng và sự thay đổi tính chất trong quá trình chiếu sáng. Cảm quang âm khi bị chiếu sáng trở nên không bị hoà tan trong các dung môi tương ứng. Còn các cảm quang dương thì ngược lại, khi bị chiếu sáng sẽ hoà tan trong các dung môi.

Dung dịch hiện Developer cho phép hiện hình những chi tiết tạo ra trên lớp cảm quang do tác dụng của nguồn UV. Quá trình này giống như quá trình rửa ảnh trong kỹ thuật nhiếp ảnh. Ở mặt nạ đầu tiên quá trình quang khắc được thực hiện khá đơn giản: đặt phiến silicon lên gá, thiết lập các điều kiện cần thiết như chân không, khí nén, chế độ tiếp xúc, công suất UV, thời gian chiếu sáng … và chiếu sáng. Tuy vậy để chế tạo một mạch tổ hợp người ta phải dùng tới nhiều bộ mặt nạ khác nhau. Để các chi tiết trên mặt nạ, trên phiến silicon của lần chế tạo trước đó (với một mặt khác trong cả bộ) trùng khít lên những chi tiết của mặt nạ hiện tại người ta phải dùng một kỹ thuật gọi là kỹ thuật đồng chỉnh (so mask hay mask aligner). Kỹ thuật này được thực hiện thông qua những dấu hiệu gọi là dấu so (mask marks) với sự trợ giúp quang học (kính hiển vi, CCD camera…) và hệ vi chỉnh cơ khí theo các chiều X,Y và chỉnh méo. Thông qua những dấu so đặc biệt này người ta có thể chắc chắn được rằng mọi chi tiết trên phiến silicon nhận được từ các mặt nạ khác nhau là trùng khít lên nhau. Trong quá trình chế tạo photođiốt chúng ta sẽ sử dụng một bộ 03 mặt nạ.

Hiện nay mật độ bóng bán dẫn trên một chíp ngày một tăng nên ngoài kỹ thuật quang khắc còn nhiều kỹ thuật khác cho phép khắc lên trên lớp cảm quang những chi tiết với độ phân giải và mức độ tinh vi tốt hơn rất nhiều như kỹ thuật e-beam lithography (kỹ thuật khắc dùng chùm điện tử), hoặc tia X.

Ăn mòn

Trong cộng nghệ vi điện tử trên cơ sở silicon là một kỹ thuật rất hay được sử dụng. Có hai phương pháp ăn mòn chính là : ăn mòn ướt và ăn mòn khô.Ăn mòn ướt

Đây là kỹ thuật thông dụng nhất trong công nghệ bán dẫn. Ngay từ công đoạn phiến vừa mới được cưa ra khỏi thỏi silion từ nhà máy sản xuất phiến, các hóa chất đã được sử dụng để mài nghiền và đánh bóng cuối cùng chúng ta thu được một tấm silicon phẳng và nhẵn. Đối với những thiết bị đơn lẻ hoặc mạch tích hợp có kích thước đủ lớn (> 3 µm), hoá chất ăn mòn được sử dụng để khắc những hoạ tiết và mở cửa sổ trên lớp vật liệu điện môi.Ăn mòn khô

Trong kỹ thuật ăn mòn khô, tấm silicon được đưa vào trong buồng chân không, sau đó hỗn hợp khí dùng cho ăn mòn được đưa vào trong buồng phản ứng. Ở chân không thích hợp, dưới tác dụng của nguồn cao tần, khí ăn mòn bị ion hoá và chúng ta thu được hỗn hợp plasma của khí nói trên bao gồm các ion F+ do đó SiO2 hoặc Si … bị ăn mòn và tạo ra các sản phẩm phản ứng tương ứng.Nhờ kỹ thuật này mà chúng ta có thể mang lại kỹ thuật ăn mòn vật liệu với hệ số tỷ lệ d/w (sâu/cao) rất lớn. Tuỳ theo độ dầy và vật liệu mà người ta chọn các chế độ ăn mòn khác nhau. Với kỹ thuật này các hãng sản xuất lớn có thể phân đoạn thiết bị dành riêng cho quá trình ăn mòn “nông” với một vài micromet chiều sâu cho tới thiết bị có thể ăn mòn qua tấm silicon (cỡ 400 micrô-mét) chỉ trong hai giờ. Thông tin thêm về lý thuyết hoặc kỹ thuật ăn mòn khô có thể tìm thấy tại www.stsystems.com và www.adixen.com là hai nhà sản xuất thiết bị ăn mòn khô nổi tiếng nhất hiện nay.

Kỹ thuật màng mỏng – chủ yếu để tạo những lớp vật liệu có bề dày như mong muốn lên trên một lớp vật liệu khác. Đây là quá trình đòi hỏi khá nhiều kiến thức bổ xung như kỹ thuật chân không, cấu trúc vật liệu…Các kỹ thuật cơ bản để tạo màng mỏng ở đây gồm hai phương pháp – vật lý và hoá học. Phương pháp vật lý bao gồm: phun xạ (sputtering), bốc bay nhiệt (evaporation), phương pháp phun tĩnh điện…. Trong khi đó phương pháp hoá học có: lắng đọng hoá học pha hơi (CVD), lắng đọng hoá học pha hơi áp suất thấp (LPCVD), và Sol-gel.

Đo đạc và khảo sát thông số công nghệ - đây là giai đoạn sau khi phiến silicon đã đi qua các bước công nghệ trong phòng sạch. Ở khâu này người kỹ sư cần xác định các đặc tuyến I-V, C-V hoặc điện trở (R), dòng dò, chế độ làm việc.…của linh kiện. Lúc này, các chíp vẫn nằm trên phiến. Để có thể tiến hành các bước tiếp sau, người kỹ sư phải cắt rời các chíp trên tấm silicon, và ở giai đoạn này chíp còn được gọi là “die”.

Khâu đóng vỏ - kỹ thuật hàn dây và hàn chip

“Đây là một công đoạn không cần đòi hỏi có các thiết bị máy móc hiện đại chính vì vậy các nhà sản xuất vừa và nhỏ hoàn toàn tự chủ động”

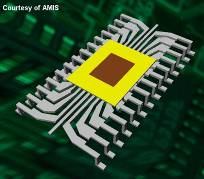

Như đã nói ở trên IC sau khi được chế tạo nằm trên tấm silion, được cắt ra và gắn lên trên các thành phần mạch tích hợp. Lúc này mỗi chíp đơn được gọi là DIE (tạm gọi là chíp trần). Trong ảnh là một chíp trần của một cấu trúc MOS (Metal-Oxide-Semiconductor), một cấu trúc transistor rất phổ biến trong chế tạo vi mạch điện tử, (nguồn www.vlsi.uwaterloo.ca) – các chân chíp bằng Au hoặc Al màu sáng ở phía ngoài. Rõ ràng những thiết kế rất nhỏ với mỗi chiều khoảng 1 mm đến vài trăm micrô-mét, việc nối dây cho các chíp này để lấy tín hiệu ra là điều không dễ dàng chút nào. Công nghệ thay đổi hàng tháng, hàng tuần thậm chí hàng ngày, mô tả toàn bộ quá trình đóng vỏ trong một vài trang giấy là điều không thể. Ở trong phạm vi đề tài này chúng tôi chỉ mạn phép được đưa ra những thông tin đơn giản nhất trong quá trình đóng vỏ chíp đó là hàn chíp và hàn dây. Để có thể nối dây, cấp nguồn cho chíp hoạt động (nghĩa là có chíp thành phẩm) chúng ta phải đi qua các công đoạn: 1. Hàn chíp trần (die attach); 2. Hàn dây (wire bonding); 3. Kiểm tra chất lượng của mối hàn (pull test). Như vậy có thể hiểu đây là ba bước cơ bản để chúng ta có thể "giao tiếp được với chip một cách dễ dàng".

Hàn chíp trên đế (Die attach)

Chíp trần, sau khi cắt rời khỏi tấm silicon, được xếp vào trong các khay và sau đó được hàn trên các khung chế tạo sẵn (leadframe-ảnh bên là Leadframe của Alcatel Microelectronics) mà thông qua đó chúng ta có thể tháo lắp chíp trên các mạch điện tử một cách dễ dàng . Ở công đoạn này mỗi nhà sản xuất sẽ lựa chọn cho mình những dây truyền công nghệ phù hợp với công suất sản xuất cũng như khả năng kinh tế. Trừ những nhà chế tạo lớn, phần lớn các công ty nhỏ và vừa thường lựa chọn các thiết bị hàn die nhân công (manual) hoặc bán tự động. Ở công đoạn này, chíp trần được gắp bằng bút chân không hoặc kẹp chân không (ảnh). Kỹ thuật này cho phép giữ chíp một cách chắc chắn đồng thời không làm tổn hại đến bề mặt chíp.Ở một số thiết bị (như của hãng WESTBOND), kỹ sư chế tạo máy đã tích hợp thêm một động cơ vào đầu gắp chân không, cho phép đặt chíp vào đúng vị trí của leadframe bằng cách chỉnh méo dưới kính hiển vi quang học hoặc CCD camêra. Hai kỹ thuật thường được sử dụng để gắn die lên trên leadframe đó là kỹ thuật eutectic và kỹ thuật dùng keo dính.

Kỹ thuật hàn dùng chất keo dính

Ở kỹ thuật này người ta hay sử dụng các hợp chất có tính chất bám dính tốt như polyimide, epoxy hoặc keo bạc làm vật liệu hàn khi gắn chíp lên leadframe. Sau khi xác định được vị trí tương thích giữa die và cấu hình trên leadframe, die sẽ được đẩy ra khỏi bút chân không, nén lên trên bề mặt của epoxy và quá trình hàn kết thúc.Kỹ thuật hàn eutectic, thường được ứng dụng trong đóng gói kín, sử dụng hợp kim cùng tinh để gắp die lên trên leadframe. Kỹ thuật hàn tiên tiến này dựa trên việc sử dụng vật liệu hàn tạo ra hợp kim cùng tinh ở một điều nhiệt độ đặc biệt nào đó, và điểm nóng chảy của hợp kim thường thấp hơn khi nó ở dạng kim loại đơn lẻ. Hợp kim Au-Si, Au-Sn hoặc Pd-Si thường được sử dụng rộng rãi trong kỹ thuật này. Để gắn được die lên leadframe đầu tiên người ta phủ một lớp vàng với độ dầy phù hợp lên trên bề mặt leadframe hoặc die).

Trong quá trình hàn, nhiệt độ cao sẽ làm khuếch tán các phân tử silic từ bề mặt die lên lớp vàng của leadframe, tạo ra cùng tinh Au-Si (ví dụ, hợp kim Au-Si với 2.85% Au có điểm nóng chày ở 3630C). Khi hàn người ta sẽ nâng nhiệt độ cao hơn Tm một chút, thường là cỡ 10°C so với nhiệt độ eutectic dẫn đến sự liên khuếch tán giữa chất rắn và chất lỏng ở bề mặt phân cách. Hợp kim eutectic sau đó hoá rắn và được làm lạnh. Hợp phần, điểm cùng tinh của một một số hợp kim được liệt kê trong bảng dưới đây.

Để tối ưu hoá việc hàn chíp, người ta đưa thêm vào chế độ 'mài' được thực hiện bởi một bộ phát siêu âm, tác dụng lên trên cần hàn, dao động với biên độ cỡ vài micrô-mét. Điều này làm tăng độ cọ xát giữa chíp với lớp vàng trên leadframe làm cho quá trình tạo cùng tinh diễn ra dễ dàng hơn.

Đến đây, chip đã được gắn chắc chắn trên bề mặt của leadframe, điều chúng ta cần làm hiện nay là nối dây từ chân các chíp này ra chân của leadframe.

Kỹ thuật hàn dây (wire bonding)

Không giống như hàn dây thiếc trên các linh kiện điện tử, hàn dây chíp là một việc làm đòi hỏi tính kiên nhẫn và sự hiểu biết về cấu trúc IC. Vật liệu hàn ở đây thường là hợp kim Au hoặc Al có đường kính mặt cắt ngang tiêu chuẩn cỡ 25 micromét, Có hai phương pháp gắn sợi dây lên những mối hàn vô cùng nhỏ bé đó là: phương pháp hàn ép nhiệt (thermocompression bonding - TC) và phương pháp hàn dùng diêu âm (ultrasonic bonding- US).Phương pháp TC được phát triển tại phòng thí nghiệm Bell (Hoa Kỳ) phục vụ cho ngành vi điện tử từ 1957, và mãi đến những năm 1960 mới được thay thế bằng phương pháp hàn dùng siêu âm. Phương pháp hàn TC dùng lực nén khi hàn, nhiệt độ cao trong điều kiện chân không hoặc khí trơ (N2, hoặc Ar) để tạo ra mối hàn.

Kỹ thuật hàn dùng siêu âm (Ultrasonic Technique)

Mối hàn, trong phương pháp này, nhận được nhờ tương tác của các yếu tố: lực chân không, áp suất, nhiệt độ và thời gian. Khi hàn, dây hàn được đặt lên trên mối hàn (bonding pad). Tần số siêu âm cộng, lực nén cộng với sự cọ sát ở điểm đầu hàn tiếp xúc với mối hàn đầu tiên làm sạch điểm tiếp xúc giữa hai vật liệu cần hàn (tẩy bỏ lớp oxít bề mặt) sau là làm tăng nhiệt độ ở khu vực đó dẫn đến có sự khuếch tán vào nhau giữa các vật liệu. Ví dụ máy hàn của công ty WESTBOND sử dụng một bộ phát siêu âm kênh đôi, hoạt động ở tần số 63 KHz được điều khiển bởi vi xử lý Motorola 68000 cho các loại máy hàn nhân công (hay vi xử lý Intel Pentium IV theo hệ điều hành Microsoft Windows® XP Professional cho các loại máy hàn tự động), thời gian phát xung và công suất xung có thể thay đổi một cách đơn giản, biên độ dao động ở chế độ cọ sát (scrubs mode) cỡ vài chục micromet xung quanh vị trí cần hàn. Trong kỹ thuật hàn dùng siêu âm, hình dạng mối hàn sẽ quy định cấu hình của đầu hàn – đó là các phép hàn tròn (ball bonding – mối hàn có dạng cầu) và phép hàn dẹt (wedge bonding – mốt hàn có dạng dẹt). Dưới tác dụng của xung siêu âm và lực nén, dây hàn bị nén dẹt và dính vào điểm hàn.

Trong kỹ thuật hàn tròn, trước tiên người ta phải tạo ra đầu dây hàn thành dạng hình cầu bằng cách đưa qua bên dưới đầu dây một thanh quệt, độ chênh lệch cao về điện thế giữa thanh quệt này với đầu dây sẽ tạo ra một tia lửa điện một đầu mối hàn được cố định, dây hàn được làm nóng chảy và tạo hình dưới dạng cầu. Sau đó kim hàn được mang đến bề mặt hàn được gia nhiệt tạo ra mối hàn thứ nhất. Mối hàn thứ hai được hoàn thành giống như ở kỹ thuật hàn dẹt. Kỹ thuật hàn tròn có ưu điểm là cho phép hàn trên những IC có kiến trúc phức tạp, nhiều lớp vì sau mối hàn thứ nhất, người kỹ sư có thể quay sợi dây hàn theo hướng anh ta muốn mà không sợ làm đứt dây hàn, đồng thời phương pháp đi dây ở kỹ thuật hàn tròn là theo chiều thẳng đứng (90°) sẽ tránh được hiện tượng đứt dây khi hàn.

Ngoài hai kỹ thuật trên còn có nhiều kỹ thuật khác như Flip-Chip (hàn lật), hoặc TAB (Tape-automated bonding - thuật ngữ mà kỹ sư Việt Nam hay dùng là: chíp dán).

Kiểm tra mối hàn (Pull Test)

Để đảm bảo chất lượng mối hàn người kỹ sư luôn phải kiểm tra xem tiếp xúc giữa dây hàn và mối hàn có tốt hay không. Phương pháp kiểm tra mối hàn thông dụng nhất là phương pháp kéo (Pull Test). Một móc được đưa vào dưới sợi dây hàn giữa hai mối hàn, môtơ – dưới điều khiển của vi xử lý – sẽ kéo móc câu này lên với lực tác dụng có thể thay đổi được. Dữ liệu lối ra trên máy tính sẽ cho người kỹ sư biết được mối hàn có tốt hay không.

Hai chế độ kiểm tra có thể sử dụng ở đây là chế độ phá huỷ (còn gọi là destruct) và không phá huỷ (còn gọi là non-destruct) mẫu. Ở chế độ kiểm tra không phá huỷ mẫu, dựa vào lực liên kết mối hàn trên những vật liệu biết trước như Au hoặc Al, người ta sẽ đặt lực kéo vào móc câu với giá trị nhỏ hơn lực làm đứt mối liên kết đó.

Công nghệ đóng vỏ

Công đoạn đóng vỏ là công đoạn cuối cùng, tùy thuộc vào các cách tạo chân IC để có thể sử dung các công nghệ đóng vỏ khác nhau, đóng vỏ trong môi trường chân không hoặc khí hiếm được áp dụng cho loai IC có chật lượng cao

(trong giai đoạn này, chúng ta có thể sử dụng các sản phẩm như của công ty Polaris), kiểm tra độ ổn định của chíp và một số công đoạn thử nghiệm khác trước khi đưa vào sử dụng.